Product Summary

The XCR5064C-10VQ44C is a CPLD. The device combines high speed and zero power in a 64 macrocell CPLD. With the FZP design technique, the XCR5064C-10VQ44C offers true pin-to-pin speeds of 7.5 ns, while simultaneously delivering power that is less than 100 μA at standby without the need for turbo bits or other power down schemes. By replacing conventional sense amplifier methods for implementing product terms (a technique that has been used in PLDs since the bipolar era) with a cascaded chain of pure CMOS gates, the XCR5064C-10VQ44C dynamic power is also substantially lower than any competing CPLDz. The XCR5064C-10VQ44C is the first TotalCMOS PLD, as it uses both a CMOS process technology and the patented full CMOS FZP design technique.

Parametrics

XCR5064C-10VQ44C absolute maximum ratings: (1)VCC, Supply voltage: -0.5 to 7.0 V; (2)VI, Input voltage: -1.2 to VCC+0.5 V; (3)VOUT, Output voltage: -0.5 to VCC+0.5 V; (4)IIN, Input current: -30 to 30 mA; (5)IOUT, Output current: -100 to 100 mA; (6)TJ, Maximum junction temperature: -40 to 150℃; (7)Tstr, Storage temperature: -65 to 150℃.

Features

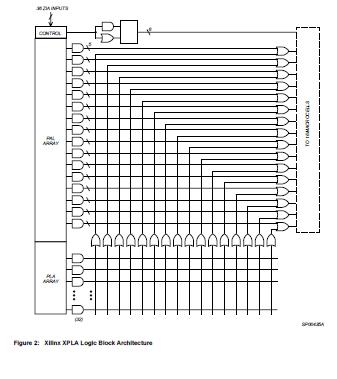

XCR5064C-10VQ44C features: (1)Support for complex asynchronous clocking; (2)Innovative XPLA?architecture combines high speed with extreme flexibility; (3)1000 erase/program cycles guaranteed; (4)20 years data retention guaranteed; (5)Logic expandable to 37 product terms; (6)PCI compliant; (7)Advanced 0.5?E2CMOS process; (8)Security bit prevents unauthorized access; (9)Design entry and verification using industry standard and Xilinx CAE tools; (10)Reprogrammable using industry standard device programmers; (11)Available in PLCC and VQFP packages; (12)Available in both Commercial and Industrial grades.

Diagrams

|

XCR5032 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XCR5032C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XCR5064C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XCR5128 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XCR5128C |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)