Product Summary

The HYB25DC512160DE-5 is a type of 512-Mbit Double-Data-Rate SDRAM with a high-speed CMOS, dynamic random-access memory containing 536,870,912 bits. It is internally configured as a quad-bank DRAM. The HYB25DC512160DE-5 SDRAM uses a double-data-rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2n prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins.

Parametrics

HYB25DC512160DE-5 maximum ratings: (1)Voltage on I/O pins relative to VSS: –0.5 to VDDQ + 0.5 V; (2)Voltage on inputs relative to VSS: -1 to +3.6 V; (3)Voltage on VDD supply relative to VSS: –1 to +3.6 V ; (4)Voltage on VDDQ supply relative to VSS: –1 to +3.6 V ; (5)Operating temperature (ambient): 0 to +70 ℃; (6)Storage temperature (plastic): –55 ℃ +150℃; (7)Power dissipation (per SDRAM component): 1 W; (8)Short circuit output current: 50 mA.

Features

HYB25DC512160DE-5 features: (1)Double data rate architecture: two data transfers per clock cycle; (2)Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver; (3)DQS is edge-aligned with data for reads and is center-aligned with data for writes; (4)Four internal banks for concurrent operation; (5)Data mask (DM) for write data; (6)DLL aligns DQ and DQS transitions with CK transitions; (7)CAS Latency: 1.5 (DDR200 only), 2, 2.5, 3; (8)Auto Precharge option for each burst access; (9)Auto Refresh and Self Refresh Modes.

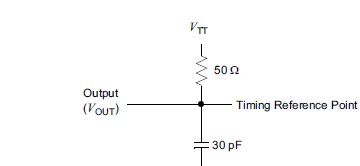

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

HYB25DC512160DE-5 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYB25DC512160DE-5A |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)